Page 14 - MWJC_SepOct2017_eMag

P. 14

CoverFeature х░БщЭвф╕УщвШ

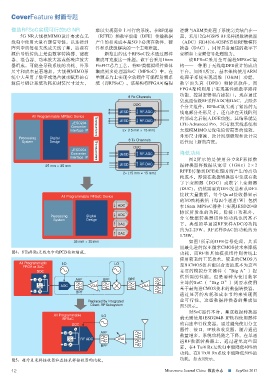

хАЯхКйRFSoCхоЮчО░хПпшбМчЪД5G NR щЪ╛ф╗ехоЮчО░хХЖф╕Ъф╕КхПпшбМчЪДч│╗ч╗ЯуАВхЬиRFхЙНчлп щА╗ш╛Сф╕ОARMч▒╗хдДчРЖхнРч│╗ч╗ЯхоМч╛Оч╗УхРИхЬиф╕А

5G NRхдзшзДцибMIMOшо╛шобшжБц▒ВхЬицЧа я╝ИRFFEя╝ЙхТМцХ░хнЧхЙНчлпя╝ИDFEя╝Йф╝аш╛УцХ░цНо ш╡╖я╝МщЗЗчФи12ф╜Н4GSPS RFщЗЗца╖цибцХ░ш╜мцНвхЩи

ч║┐чФ╡ф╕нф╜┐чФихдзщЗПцЬЙц║Рф┐бхП╖щУ╛я╝Мф╗еш┐ЮцОехИ░ ф║зчФЯчЪДчЫ╕хЕ│цИРцЬмцШп5Gф╕нх┐Ещб╗хЬиш╜пф╗╢уАБчбм я╝ИADCя╝ЙхТМ14ф╜Н6.4GSPSчЫ┤цОеRFцХ░цибш╜м

щШ╡хИЧф╕нчЪДцпПца╣хдйч║┐цИЦхдйч║┐хнРщЫЖуАВш┐Щф║ЫцЬЙ ф╗╢хТМч│╗ч╗Яч║зшзгхЖ│чЪДф╕Аф╕кф╕╗шжБщЪ╛щвШуАВ цНвхЩия╝ИDACя╝Йя╝МхРМцЧ╢хЕ╖хдЗцЬАф╜│чЪДцХ░хнЧф╕Л

ц║Рф┐бхП╖щУ╛ф╝ач╗Яф╕КцШпчФ▒цХ░хнЧш╜мцНвхЩиуАБц╗дц│в цЦ░цОихЗ║чЪДш┐Щф╕кRFSoCцКАцЬпщАЪш┐ЗхЩиф╗╢ хПШщвСхТМф╕КхПШщвСф┐бхП╖хдДчРЖшГ╜хКЫуАВ

хЩиуАБц╖╖хРИхЩиуАБхКЯчОЗцФ╛хдзхЩицИЦф╜ОхЩкхг░цФ╛хдз щЫЖцИРхПпхЕЛцЬНш┐Щф╕АщЪ╛щвШуАВшпех╣│хП░щЗЗчФи16nm шпеRFSoCщЗЗчФихЕихПпч╝ЦчиЛMPSoCцЮ╢

хЩич╗ДцИРя╝МхПпшГ╜ф╝Ъхп╝шЗ┤ч│╗ч╗ЯчЪДхКЯшАЧуАБхдЦх╜в FinFETшКпчЙЗх╖ешЙ║я╝Мх░ЖRFч▒╗цибцЛЯч╗Дф╗╢цХ┤ф╜У цЮДтАФтАФф╕АчзНчФиф║ОцЧач║┐чФ╡DFEшо╛шобчЪДцИРхКЯ

х░║хп╕хТМцИРцЬмцШ╛шСЧхвЮхКауАВхдзшзДцибMIMOч│╗ щЫЖцИРхИ░хдЪхдДчРЖхЩиSoCя╝ИMPSoCя╝Йф╕ня╝МхЬи х╣│хП░уАВхжВхЫ╛1цЙАчд║я╝МхЯ║цЬмцЮ╢цЮДф╜┐чФиARM

ч╗Яф╕нхдзщЗПчФиф║ОцХ░хнЧцИЦц╖╖хРИц│вцЭЯш╡Лх╜вчЪДцЬЙ хНХщвЧшКпчЙЗф╕КхоЮчО░хЕиш╜пчбмф╗╢хПпч╝ЦчиЛх░ДщвСч│╗ хдДчРЖхнРч│╗ч╗ЯхоЮчО░ш┐Рч╗┤я╝ИO&Mя╝ЙхКЯшГ╜уАБ

ц║Рф┐бхП╖щУ╛шойч│╗ч╗ЯхКЯшАЧхТМх░БшгЕх░║хп╕ш┐Зхдзя╝М ч╗Яя╝ИхН│RFSoCя╝ЙуАВшпецЮ╢цЮДх░ЖFPGAхПпч╝ЦчиЛ цХ░хнЧщвДхд▒чЬЯя╝ИDPDя╝ЙхТМхНПшоош╜пф╗╢я╝МшАМ

FPGAцЮ╢цЮДхИЩчФиф║ОхоЮчО░щлШцАзшГ╜цХ░хнЧш╖пх╛Д

хКЯшГ╜уАБцОзхИ╢щА╗ш╛СхТМщлШщАЯцОехПгуАВчО░хЬищАЪш┐З

8 Rx Channels

щЫЖцИРщАЪф┐бч║зRFщЗЗца╖ADCхТМDACя╝МхО╗щЩдхдЪ

DDC

ф╕кхИЖчлЛч╗Дф╗╢я╝МRFSoCцЧвхоЮчО░ф║Жч┤зхЗСчЪДцЧа

JESD RF-ADC ч║┐чФ╡щГихИЖхдЦх╜вх░║хп╕я╝Мш┐ШхЕБшо╕хЬихдйч║┐щШ╡хИЧ

All Programmable MPSoC Device хЖЕщГицИЦф╣ЛхРОх╡МхЕеDFEхКЯшГ╜уАВхЕ╢ч╗УцЮЬх░▒цШп

JESD RF-DAC

JESD204 LTE-Advanced ProуАБ5GцЬЙц║Рхдйч║┐ч│╗ч╗ЯхТМ

Converter Transceivers

Interface IP 2├Ч (15 mm ├Ч 15 mm) хдзшзДцибMIMOцЧач║┐чФ╡ш┐лхИЗщЬАшжБчЪДшГ╜цХИуАБ

хдЦх╜вх░║хп╕ч╝йхЗПуАБшо╛шобхСицЬЯч╝йчЯнхТМшо╛шобчБ╡

Processing Digital

System Design 8 Tx Channels ц┤╗цАзш┐Иф╕КцЦ░чЪДщлШх║жуАВ

DUC

JESD204 Transceivers

Converter JESD RF-ADC щЩНф╜ОхКЯшАЧ

Interface IP

хЫ╛2цЙАчд║чЪДцШпф╜┐чФихИЖчлЛRFщЗЗца╖цХ░

35 mm ├Ч 35 mm JESD RF-DAC цНош╜мцНвхЩих░ЖцХ░цНоф╗Охо╜х╕жя╝И1GHzя╝Й2├Ч2

RFFEф╝аш╛УхИ░DFEхдДчРЖцЧ╢цЙАф║зчФЯчЪДщлШхКЯ

2├Ч (15 mm ├Ч 15 mm)

шАЧцИРцЬмуАВхН│ф╛┐хЬицХ░цНош╜мцНвхЩиф╕нщЫЖцИРцЬЙцХ░

хнЧф╕ЛхПШщвСхЩия╝ИDDCя╝ЙцИЦцХ░хнЧф╕КхПШщвСхЩи

(DUC)я╝Мф╗НчД╢щЬАшжБхРСDFEхПСщАБхТМф╗ОDFE

All Programmable RFSoC Device цОецФ╢хдзщЗПцХ░цНоуАВцпПф╕кQuadцОецФ╢хЩицШ╛чд║

чЪДI/OхКЯшАЧцХ░хА╝я╝ИцпПхЫЫф╕кщАЪщБУ1Wя╝ЙхМЕцЛм

ADC хЬи16nm MPSoCхЩиф╗╢ф╕КхоЮчО░JESD204B

хНПшооцЙАхПСчФЯчЪДхКЯшАЧуАВщЩдцОехПгхКЯшАЧхдЦя╝М

Processing Digital ADC

System Design хИЖчлЛцХ░цНош╜мцНвхЩич╗Дф╗╢чЪДхКЯшАЧф╣Ях▒ЕщлШф╕Н

DAC ф╕ЛуАВхЕ╕хЮЛчЪДхНХщАЪщБУRFщЗЗца╖ADCчЪДхКЯшАЧ

ч║жф╕║2.25Wя╝МRFщЗЗца╖DACчЪДхКЯшАЧч║жф╕║

DAC

1.75WуАВ

35 mm ├Ч 35 mm хжВхЫ╛1цЙАчд║чЪДDFEф┐бхП╖хдДчРЖя╝МхЕ╢щЗЗ

чФицЬАхЕИш┐ЫчЪДц╖▒ф║Ъх╛оч▒│CMOSцКАцЬпцЭещЩНф╜О

хЫ╛4я╝Ъ8 Tx/8 RxцЧач║┐чФ╡ф╕нчЪДPCBщЭвчзпч╝йхЗПуАВ хКЯшАЧя╝МшАМRFхТМхЕ╢ф╗ЦцибцЛЯч╗Дф╗╢хИЩф╝ач╗Яф╕К

ф╜┐чФиш╛ГшАБчЪДх╖ешЙ║цКАцЬпуАВш╛ГшАБчЪДCMOSф╣Г

All Programmable LO LO шЗ│BiCMOSцКАцЬпшГ╜ф╗ехРИщАВчЪДцИРцЬмф╕║ш┐Щф║Ы

FPGA or SoC

DDC ф╕╗шжБчЪДцибцЛЯхИЖчлЛхЩиф╗╢я╝ИтАЬBig AтАЭя╝ЙцПР

ф╛ЫцЙАщЬАчЪДцАзшГ╜уАВф╜ЖцШпшжБш╜мф╕║ф╜┐чФицХ░хнЧ

AAF BPF BPF

0┬░ LNA ф╕╗хп╝чЪДSoCя╝ИтАЬBig DтАЭя╝ЙхИЩшжБц▒Вф╜┐чФи

90┬░ ADC VGA хЯ║ф║ОцЬАхЕИш┐ЫCMOSцКАцЬпчЪДцХ░цНош╜мцНвхЩия╝М

BPF

щАЪш┐ЗцШ╛шСЧчЪДхКЯшАЧхТМцИРцЬмшКВч║жцЭехоЮчО░хХЖ

Replaced by Integrated ф╕ЪхПпшбМцАзуАВш┐Щф║ЫцХ░цНош╜мцНвхЩичЪДщЫЖцИРхжВ

Direct-RF Subsystem хЫ╛3цЙАчд║уАВ

хп╣SoCхЩиф╗╢цЬмш║ля╝МщЫЖцИРцХ░цНош╜мцНвхЩи

All Programmable LO

RFSoC х░▒цЧащЬАф╜┐чФиJESD204B IPца╕хТМф╜┐чФихЩиф╗╢

DDC чЪДщлШщАЯф╕▓шбМцФ╢хПСхЩиуАВщАЪш┐ЗщБ┐хЕНф╜┐чФихИЖчлЛ

хЩиф╗╢уАБцОехПгуАБIPца╕хТМцФ╢хПСхЩия╝МщЪПчЭАщАЪщБУ

AAF

цХ░щЗПхвЮхдЪя╝Мч│╗ч╗ЯхКЯшАЧщЪПф╣Лф╕ЛщЩНуАВхЬихНХщАЪ

0┬░ LNA

90┬░ RF ADC щБУRFцХ░цНош╜мцНвхЩиф╕Кя╝МщАЪш┐ЗщБ┐хЕНш┐Щф║ЫхЫа

BPF ч┤ая╝МхЬи4 Tx/4 RxцЧач║┐чФ╡ф╕ншГ╜щЩНф╜О40%чЪД

хКЯшАЧя╝МхЬи8 Tx/8 Rxч│╗ч╗Яф╕ншГ╜щЩНф╜О50%чЪД

хЫ╛5я╝Ъш╢ЕхдЦх╖ощЗЗца╖цОецФ╢хЩихТМчЫ┤цОещЗЗца╖цОецФ╢хЩичЪДцпФш╛ГуАВ хКЯшАЧя╝МхжВшби1цЙАчд║уАВ

12 Microwave Journal China х╛оц│вцЭВх┐Ч Sep/Oct 2017

170901_Test2_MJC_CN.indd 1 9/1/17 1:36 PM