Page 30 - MWJC_SepOct2017_eMag

P. 30

TechnicalFeature ТіђТю»уЅ╣тєЎ

т»╣С║јСИђу│╗тѕЌу║ДУЂћтЁЃтЎеС╗ХуџёСИЅжўХТѕфУји тцДтЎетљёу║ДуџёжЮЎТђЂтиЦСйюуѓ╣С╝џжџЈуЮђУЙЊтЄ║тіЪујЄ

уѓ╣№╝їС╝ау╗ЪуџёУАеУЙЙт╝ЈС╝џт»╝УЄ┤тюеУЙЃтцДуџёУЙЊтЁЦ ућхт╣│тЈЉућЪтЈўтїќ№╝їТЃ│УдЂУјитЙЌтЁиТюЅТюђСй│EVM

тіЪујЄу║ДтѕФУїЃтЏ┤тєЁт»╣У»»ти«уЪбжЄЈт╣Ёт║дтЂџтЄ║уџё уџёт░ёжбЉтГљу│╗у╗ЪУ«ЙУ«АтЈўтЙЌжЮътИИтЁиТюЅТїЉТѕў жЏєТѕљућхУи»У«ЙУ«А/ТхІжЄЈ

жбёТхІСИЇТў»жЮътИИтЄєуА«№╝џ ТђД№╝їжЃетѕєтјЪтЏаТў»ТаИт┐ЃжЏєТѕљућхУи»тњїтіЪујЄТћЙ

тцДтЎеС╣ІжЌ┤уџётіЪујЄућхт╣│тњїжЮЎТђЂућхТхЂтЈ»С╗Цтйб

ТѕљтцџуДЇу╗ётљѕ№╝їтЈ»УЃйт»╝УЄ┤жЦ▒тњїтіЪујЄућхт╣│уЏИ жЮъу║┐ТђДУАетЙЂ

тљї№╝їСйєEVMТђДУЃйтЇ┤тцДСИЇСИђТаисђѓ

У«Итцџуј░С╗БТЌау║┐жђџС┐Ау│╗у╗ЪжЄЄућеТГБС║цжбЉ

тЁХСИГG 1 Тў»уггСИђу║ДтбъуЏі№╝їI P3,i УАеуц║уггi тѕєтцЇуће№╝ѕOFDM№╝Ѕ№╝їтЁиТюЅ64-QAMТѕќТЏ┤ EVMС╗┐уюЪТхІУ»ЋтЈ░

у║ДуџёСИЅжўХТѕфУјиуѓ╣сђѓ жФўжўХУ░ЃтѕХС╗ЦтЈі40MHzТѕќТЏ┤жФўтИдт«йсђѓу│╗у╗Ъ (a)

УђЃУЎЉтЏЙ1ТЅђуц║уџёуЏИТјДжўхтЈЉт░ёТю║/ТјЦТћХ жђџтИИУдЂТ▒ѓEVMСИЇУХЁУ┐Є1.8%№╝їУ┐Ўт░▒жюђУдЂ

Тю║№╝ѕT/R№╝ЅтЅЇуФ»уџёу«ђтїќТАєтЏЙсђѓжЮъу║┐ТђДтЁЃ т»╣у│╗у╗ЪУ┐ЏУАїС╗ћу╗єуџёС╝ўтїќсђѓт░єСИЦУІЏуџёEVM жЏєТѕљућхУи»У«ЙУ«А/ТхІжЄЈ

С╗ХТў»тіЪујЄТћЙтцДтЎе№╝ѕPA№╝ЅтњїТаИт┐ЃжЏєТѕљућх УдЂТ▒ѓУйгтїќТѕљт«ъжЎЁуџёт░ёжбЉжЏєТѕљућхУи»У«ЙУ«АТхЂ

Уи»(IC)сђѓтљјУђЁУ┤ЪУ┤БуЏИСйЇтњїт╣Ёт║дТјДтѕХ№╝їС╗Ц уеІ№╝їт»╣С║јС║цС╗ўтЁиТюЅжФўтіЪујЄТЋѕујЄтњїС╝ўт╝ѓ

УјитЙЌуЅ╣т«џуџёТ│бТЮЪУхІтйбуЅ╣ТђДсђѓСИЇтљїС║јСИЅжўХ EVMТђДУЃйуџёу│╗у╗ЪУЄ│тЁ│жЄЇУдЂсђѓ жЮъу║┐ТђДУАетЙЂ.s2dТќЄС╗ХТЈљтЈќ

ТѕфУјиуѓ╣№╝їТаИт┐ЃжЏєТѕљућхУи»тњїтіЪујЄТћЙтцДтЎе

уџёжЮъу║┐ТђДуЅ╣ТђДжђџУ┐ЄAM-AMтњїAM-PMтіЪ тц▒уюЪтњїEVM

УЃйтіаС╗ЦТЈЈУ┐░сђѓУ┐ЎС║ЏтіЪУЃйтЈ»С╗ЦТЏ┤тЄєуА«тю░ СИ║С║єТЏ┤тЦйтю░уљєУДБAM-AMтњїAM-PM EVMС╗┐уюЪТхІУ»ЋтЈ░

ТЈЈУ┐░у│╗у╗ЪуџёжЮъу║┐ТђДуЅ╣ТђДсђѓжђџУ┐ЄAM-AM жЮъу║┐ТђДуЅ╣ТђДтЈітЁХСИјEVMуџётЁ│у│╗№╝їУ»итЈѓ (b)

тњїAM-PMтц▒уюЪТЮЦт«џС╣ЅтЏЙ1СИГуџёу«ђтЇЋтГљу│╗ УДЂтЏЙ1сђѓтЈїтљЉT/RтЅЇуФ»тїЁТІгуЪбжЄЈУ░ЃтѕХуД╗уЏИ

у╗Ъ№╝їт╣ХСИћУђЃУЎЉтѕ░ТаИт┐ЃжЏєТѕљућхУи»тњїтіЪујЄТћЙ тЎесђЂСйјтЎфтБ░ТћЙтцДтЎесђЂтіЪујЄТћЙтцДтЎетњїтЈїтљЉ тЏЙ5№╝џС╝ау╗ЪУ«ЙУ«АТхЂуеІ№╝ѕa№╝ЅтњїТЋ┤тљѕС║єEVM

С╝аУЙЊт╝ђтЁ│сђѓжђџУ┐ЄТћ╣тЈўТаИт┐ЃжЏєТѕљућхУи»СИЇтљї тѕєТъљуџёУ░ЃТЋ┤ТхЂуеІ№╝ѕb№╝Ѕсђѓ

ТћЙтцДтЇЋтЁЃуџётбъуЏі№╝їтЈ»С╗Цт»╣т╣Ёт║дтіаС╗ЦТјД

тЂЈуй«ућхтјІ=0.54V тѕХсђѓтюет░ёжбЉжбЉујЄСИІт«ъуј░тЈ»тЈўтбъуЏіТћЙтцД№╝ї ТюђтцДу║┐ТђДУЙЊтЄ║тіЪујЄсђѓСЙІтдѓ№╝їтЈ»С╗ЦСй┐ућетЏЙ3

тЂЈуй«ућхтјІ=0.56V тИИућеуџёТќ╣Т│ЋСИђУѕгТў»Тћ╣тЈўтЎеС╗ХуџётЂЈуй«№╝їС╗ј СИГуџёТЏ▓у║┐т╣ХжђЅТІЕ13dBуџётЏъжђђ№╝їУ┐ЎТаи256-

тЂЈуй«ућхтјІ=0.57V

тЂЈуй«ућхтјІ=0.58V УђїТћ╣тЈўжЮЎТђЂућхТхЂсђѓжђџУ┐ЄТћ╣тЈўжЮЎТђЂућхТхЂ№╝ї QAM OFDMуџёу║┐ТђДУЙЊтЁЦтіЪујЄтцДУЄ┤тЈ»т«џС╣Ѕ

тЂЈуй«ућхтјІ=0.59V тЎеС╗ХуџёУиет»╝С╝џтЈЉућЪтЈўтїќ№╝їућхтјІтбъуЏіС╣ЪТў» СИ║-22dBmсђѓжђџУ┐Єт░єтЂЈуй«уѓ╣С╗ј0.54VтЈўСИ║

15 тдѓТГцсђѓжЎцС║єт╣Ёт║дТјДтѕХтцќ№╝їТаИт┐ЃжЏєТѕљућхУи» 0.59V№╝їтЈ»УјитЙЌу║д12dBуџётбъуЏіТјДтѕХсђѓ

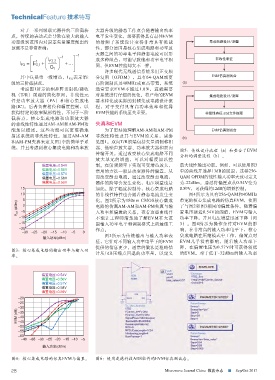

10 уџёжЮъу║┐ТђДуЅ╣ТђДС╣ЪС╝џжџЈуЮђжЮЎТђЂућхТхЂтЈЉућЪтЈў тЏЙ4ТЅђуц║СИ║тЁиТюЅ256-QAMтњї40MHz

5 тїќсђѓтЏЙ2ТЅђуц║СИ║180nm CMOSТаИт┐ЃжЏєТѕљ тИдт«йуџёТаИт┐ЃжЏєТѕљућхУи»уџёС╗┐уюЪEVM№╝їСй┐уће

P out (dBm) РђЊ5 0 ућхУи»уџёС╗┐уюЪAM-AMтњїAM-PMтц▒уюЪСИјУЙЊ С║єСИјтЏЙ2тњїтЏЙ3уЏИтљїуџётЂЈуй«ТЮАС╗ХсђѓжџЈуЮђтЂЈ

уй«ућхтјІТјЦУ┐Љ0.54Vуџёжўѕтђ╝№╝їEVMСИјУЙЊтЁЦ

тЁЦтіЪујЄтњїтЂЈуй«уџётЁ│у│╗сђѓТЪЦуюІУ┐ЎС║ЏТЏ▓у║┐т╣Х

РђЊ10 СИЇУЃйУ«ЕтиЦуеІтИѕТИЁТЦџтю░С║єУДБEVMтюетцДУїЃ тіЪујЄСИІжЎЇ№╝їт╣ХСИћућхтјІтбъуЏіУ┐ЁжђЪСИІжЎЇ№╝ѕтЏЙ

РђЊ15 тЏ┤УЙЊтЁЦтіЪујЄућхт╣│тњїУ░ЃтѕХТа╝т╝ЈСИіуџёТюђСй│тиЦ 3№╝ЅсђѓтЏЙ4ТЅђуц║СИ║ТЊЇСйюТЮАС╗Хт»╣EVMуџётй▒

РђЊ20 Сйюуѓ╣сђѓ тЊЇсђѓтюежЮътИИжФўуџёУЙЊтЁЦтіЪујЄућхт╣│СИІ№╝їТаИт┐Ѓ

РђЊ30 РђЊ25 РђЊ20 РђЊ15 РђЊ10 РђЊ5 0

тЏЙ3ТЅђуц║СИ║С╝ау╗ЪУЙЊтЄ║СИјУЙЊтЁЦтіЪујЄУАе жЏєТѕљућхУи»тюетјІу╝ЕТеАт╝ЈСИГтиЦСйю№╝їтЂЈуй«уѓ╣т»╣

УЙЊтЁЦтіЪујЄ(dBm)

тЙЂ№╝їт«Ѓжњѕт»╣СИЇтљїУЙЊтЁЦтіЪујЄућхт╣│СИІуџёEVM EVMтЄаС╣јТ▓АТюЅтй▒тЊЇсђѓжџЈуЮђУЙЊтЁЦтіЪујЄСИІ

ТЈљСЙЏуџёС┐АТЂ»ТЏ┤т░ЉсђѓжђџтИИуџётЂџТ│ЋТў»у▓ЌуЋЦС╝░ жЎЇ№╝їтюетЂЈуй«ућхтјІСИ║0.57VТЌХтЈ»УјитЙЌУЙЃСйј

тЏЙ3№╝џТаИт┐ЃжЏєТѕљућхУи»уџёУЙЊтЄ║тіЪујЄСИјУЙЊтЁЦтіЪ

ујЄсђѓ У«АС╗ј1dBтјІу╝Еуѓ╣тЏъжђђуџётіЪујЄжЄЈ№╝їС╗Цт«џС╣Ѕ уџёEVMсђѓт»╣С║јСйјС║ј-32dBmуџёУЙЊтЁЦтіЪујЄ

тЂЈуй«ућхтјІ=0.54V

тЂЈуй«ућхтјІ=0.56V

тЂЈуй«ућхтјІ=0.57V

тЂЈуй«ућхтјІ=0.58V

тЂЈуй«ућхтјІ=0.59V

РђЊ20

РђЊ25

РђЊ30

EVM (dB) РђЊ35

РђЊ40

РђЊ45

РђЊ50

РђЊ55

РђЊ60

РђЊ40 РђЊ35 РђЊ30 РђЊ25 РђЊ20 РђЊ15 РђЊ10 РђЊ5

УЙЊтЁЦтіЪујЄ(dBm)

тЏЙ4№╝џТаИт┐ЃжЏєТѕљућхУи»уџёС╗┐уюЪEVMСИјтЂЈуй«сђѓ тЏЙ6№╝џСй┐ућеТў»тЙиуДЉТіђADSУй»С╗ХуџёEVMС╗┐уюЪТхІУ»ЋтЈ░сђѓ

28 Microwave Journal China тЙ«Т│бТЮѓт┐Ќ Sep/Oct 2017